#### SHF Communication Technologies AG

Wilhelm-von-Siemens-Str. 23D • 12277 Berlin • Germany Phone +49 30 772051-0 • Fax +49 30 7531078 E-Mail: sales@shf.de • Web: http://www.shf.de

# Datasheet SHF 78210 C Synthesized Clock Generator

SHF reserves the right to change specifications and design without notice – SHF 78210 C - V001 – Feb. 12, 2014 Page 1/10

#### Description

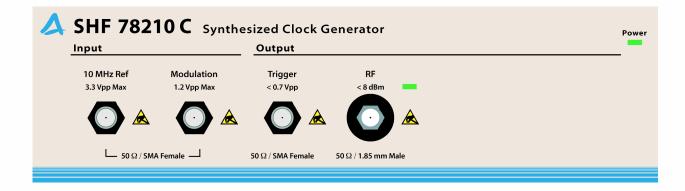

The Synthesized Clock Generator SHF 78210 C is designed to provide our BERT system customers with a suitable internal clock source at reasonable cost. It is a field replaceable plug-in module which needs to be installed in an SHF mainframe. Together with other plug-in modules from this instruments series, a modular and scalable measurement system can be put together.

It features a wide frequency range from 5 GHz to 38 GHz, a large output power range variable from –10 dBm to +8 dBm in 0.1 dB steps and it generates low jitter clock signals. For frequencies above 10 GHz, additional band-pass filtering ensures low harmonic levels. From 5 to 10 GHz, short rise time clock signals are generated in a trade-off for increased levels of higher-order harmonics.

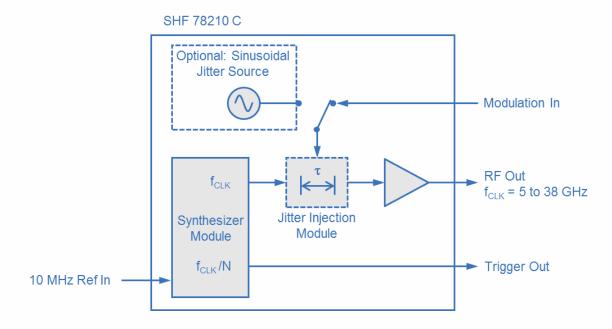

The **jitter injection** functionality is integrated for jitter stress test applications. Arbitrary jitter types may be applied to the clock signal using an external signal source, enabling various test scenarios such as data protocol compliance testing. An optional internal jitter source provides sinusoidal jitter from 10 to 400 MHz with variable jitter amplitude.

An additional **trigger output** provides a trigger signal whose frequency can be switched to a quarter or half the output frequency. The trigger remains jitter-free even if jitter injection is used.

#### **Block Diagram**

#### Features

- Output clock frequency ranges from f<sub>CLK</sub> = 5 to 38 GHz with 1 MHz resolution

- Output power adjustable from -10 to +8 dBm with 0.1 dB resolution

- External jitter modulation

- Supports three spread-spectrum clocking (SSC) modes

- 10 MHz reference input for phase locking to other instruments

- Remote programming interface for automated measurements

SHF reserves the right to change specifications and design without notice – SHF 78210 C - V001 – Feb. 12, 2014 Page 2/10

The SHF 78210 C is operated inside an SHF mainframe and controlled by an external computer (not part of the delivery). Every system comes along with the intuitive, easy to use BERT Control Center software (BCC). The BCC provides the user friendly interface for changing the device parameters.

Additionally, the instrument may be programmed remotely over the Ethernet connection for automated tests and measurements. Please refer to the SHF BERT Programming Manual.

Note that SHF also offers the compact standalone Synthesized Clock Generator SHF 78120 A. Please visit <u>www.shf.de</u> for further details.

| Synthesized Signal Generator @ 0                 |                            |                                                  |           |                |                                          |                  |                |  |  |  |

|--------------------------------------------------|----------------------------|--------------------------------------------------|-----------|----------------|------------------------------------------|------------------|----------------|--|--|--|

| SHF 78210 C Synthesized Signal Generator @ ready |                            |                                                  |           |                |                                          |                  |                |  |  |  |

|                                                  | Freq<br>32.000             | GHZ<br>GHZ                                       | 6.0       | Amplitude      |                                          | Dutput           |                |  |  |  |

|                                                  | Spread  Off Up Center Down | Spectrum<br>Deviation<br>5000<br>Frequency<br>33 | ▲ ppm     | Jitte          | Amplitude<br>10.0<br>Frequenc<br>100.000 | e<br>ps<br>y     |                |  |  |  |

| [                                                | Trigger Mode               |                                                  |           |                |                                          |                  |                |  |  |  |

| Clk/2  Trigger Frequency: 16.000 GHz  Clk/4      |                            |                                                  |           |                |                                          |                  |                |  |  |  |

| Synthesized Signal Gen                           | erator : 1.0               | Serial: 31149                                    | Option: 0 | Server: 0.78.8 | Kernel: 0                                | CPU: 51609600 Hz | Factory preset |  |  |  |

**Graphical User Interface**

#### Options

#### **Option ISJ: Internal Sinusoidal Jitter Source**

Several data communication standards require jitter tolerance and jitter transfer testing for sinusoidal jitter over a specified jitter frequency range. The optional internal sinusoidal jitter source allows stress tests for jitter frequencies ranging from 10 to 400 MHz. Jitter amplitudes up to 60 ps may be generated. The jitter amplitude is calibrated depending on the jitter frequency and on the clock frequency.

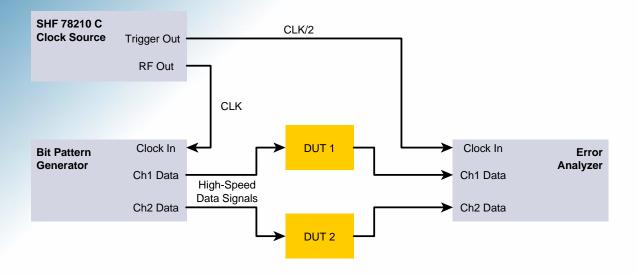

**Typical Multi-Channel Test Setup**

# **Specifications**

| Parameter                  | Symbol           | Unit   | Min.             | Тур. | Max.             | Comment                                         |

|----------------------------|------------------|--------|------------------|------|------------------|-------------------------------------------------|

| Clock Output (RF Out)      |                  |        |                  |      |                  |                                                 |

| Operating Frequency        | f <sub>CLK</sub> | GHz    | 5                |      | 38               |                                                 |

| Frequency Resolution       |                  | MHz    |                  | 1    |                  |                                                 |

| Frequency Accuracy         |                  |        |                  |      | 10 <sup>-5</sup> | Using internal reference                        |

| Frequency Stability        |                  |        | 10 <sup>-6</sup> |      | 10 <sup>-5</sup> | Ambient<br>temperature 21°C                     |

| Frequency Stability Aging  |                  | ppm    |                  |      | 3                | per year                                        |

| Output Power Level         | Pout             | dBm    | -10              |      | +8               |                                                 |

| Output Power Resolution    |                  | dB     |                  |      | 0.1              |                                                 |

| Output Power Accuracy      |                  | dB     |                  |      | 1                |                                                 |

| Harmonics/Spurious Signals |                  | dBc    |                  |      | -20              | For f <sub>CLK</sub> ≥ 10 GHz                   |

| Phase Noise                |                  | dBc/Hz |                  | tbd  |                  |                                                 |

| Jitter (RMS)               | J <sub>RMS</sub> | fs     |                  |      | 400              | On scope display (not deconvolved) <sup>1</sup> |

| Output Impedance           |                  | Ω      |                  | 50   |                  |                                                 |

| Connector                  |                  |        |                  |      |                  | 1.85 mm (V) male                                |

<sup>&</sup>lt;sup>1</sup> Measured with Agilent 86100A, 70 GHz sampling head and precision time base triggered by clock signal from RF Out.

SHF reserves the right to change specifications and design without notice – SHF 78210 C - V001 – Feb. 12, 2014 Page 4/10

| Parameter                                        | Symbol | Unit | Min. | Тур. | Max. | Comment                              |  |  |

|--------------------------------------------------|--------|------|------|------|------|--------------------------------------|--|--|

| Trigger Out                                      |        |      |      |      |      |                                      |  |  |

| Frequency                                        |        | GHz  | 1.25 |      | 19   |                                      |  |  |

| Output Amplitude                                 |        | mVpp | 400  |      | 700  |                                      |  |  |

| Output Impedance                                 |        | Ω    |      | 50   |      |                                      |  |  |

| Connector                                        |        |      |      |      |      | SMA female                           |  |  |

|                                                  |        |      |      |      |      |                                      |  |  |

| Option ISJ: Internal Sinusoidal Jitter Injection |        |      |      |      |      |                                      |  |  |

| Jitter Frequency                                 |        | MHz  | 10   |      | 400  |                                      |  |  |

| Jitter Amplitude                                 |        | ps   | 0    |      | 60   |                                      |  |  |

|                                                  |        |      |      |      |      |                                      |  |  |

| External Jitter Injection                        |        |      |      |      |      |                                      |  |  |

| Modulation Bandwidth                             |        | MHz  | 0.1  |      | 1000 |                                      |  |  |

| Modulation Amplitude                             |        | mVpp | 0    |      | 1200 | Maximum corresponds to 60 ps jitter. |  |  |

| Jitter Amplitude                                 |        | ps   | 0    |      | 60   | Peak-to-peak                         |  |  |

| Spread Spectrum Clocking |     |    |        |                |

|--------------------------|-----|----|--------|----------------|

| Modulation Frequency     | Hz  | 10 | 100 k  |                |

| Deviation                | ppm | 0  | 20,000 | Up/down/center |

Ω

50

SMA female

| 10 MHz Ref Input    |                  |     |     |    |     |            |

|---------------------|------------------|-----|-----|----|-----|------------|

| Reference Frequency | f <sub>ref</sub> | MHz |     | 10 |     |            |

| Amplitude           |                  | Vpp | 0.2 |    | 3.3 |            |

| Input Impedance     |                  | Ω   |     | 50 |     |            |

| Connector           |                  |     |     |    |     | SMA female |

| General               |    |    |   |    |                                 |

|-----------------------|----|----|---|----|---------------------------------|

| Power Consumption     | W  |    |   | 25 | Power supplied by SHF Mainframe |

| Weight                | kg |    | 4 |    |                                 |

| Operating Temperature | °C | 10 |   | 35 | Ambient temperature             |

SHF reserves the right to change specifications and design without notice – SHF 78210 C - V001 – Feb. 12, 2014 Page 5/10

Input Impedance

Connector

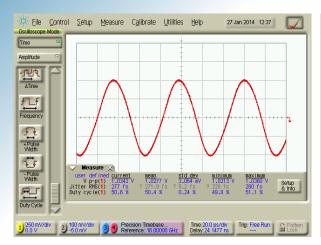

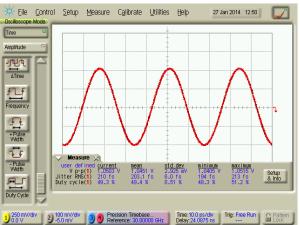

## **Typical Output Waveforms**

Clock Signal at f<sub>CLK</sub> = 16 GHz, P<sub>out</sub> = +4 dBm

Clock Signal at f<sub>CLK</sub> = 30 GHz, P<sub>out</sub> = +4 dBm

Clock Signal at f<sub>CLK</sub> = 32 GHz, P<sub>out</sub> = +4 dBm

Clock Signal at f<sub>CLK</sub> = 5 GHz

Note that for clock frequencies above 10 GHz, the signal is band-pass filtered to achieve low harmonics and a nearly pure sine wave. Below 10 GHz, however, the clock signals are amplified with subsequent amplitude clipping to shorten the rise time. In the frequency range below 10 GHz, this generates noticeable higher-order harmonics. The SHF 78210 C is optimized for clock source applications in combination with SHF BERT instruments, where a short rise time is preferred.

SHF reserves the right to change specifications and design without notice - SHF 78210 C - V001 - Feb. 12, 2014 Page 6/10

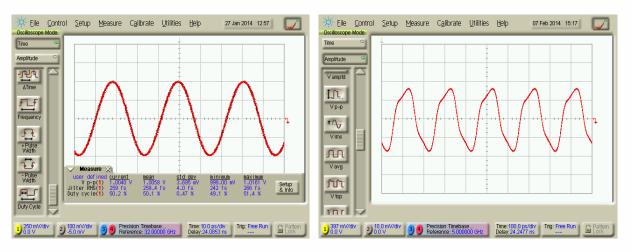

The following diagram shows typical amplitude measurement results using a power meter connected directly on the RF Out port for power settings from -10 to +8 dBm.

#### **External Jitter Injection**

For additional flexibility, arbitrary jitter modulation may be applied to the high-speed clock signal. Jitter is injected by connecting a signal source such as an arbitrary waveform generator to the external modulation input. The maximum jitter amplitude is 60 ps peak-to-peak with a modulation bandwidth of up to 1 GHz. As an example, the jitter amplitude of 60 ps corresponds to a relative jitter amplitude of 2.2 unit intervals (UI) at a bit rate of 32 Gbit/s.

The jitter amplitude is calibrated using the Trigger Output signal of the SHF 78210 C which remains jitterfree even if jitter injection is used.

In combination with an SHF Bit Pattern Generator and an Error Analyzer, the SHF 78210 C enables a complete test solution for jitter tolerance tests as required by many telecommunication standards such as 100G Ethernet and 40 GBit/s OTN, FibreChannel, InfiniBand®, PCI Express®, and Serial ATA. For further details please refer to the SHF application note "Jitter Injection using the Multi- Channel BPG", available online at <u>www.shf.de</u>.

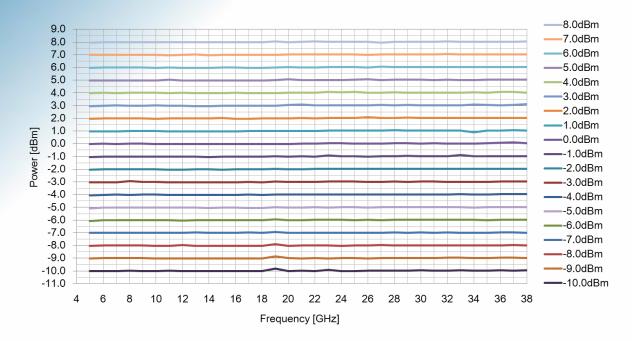

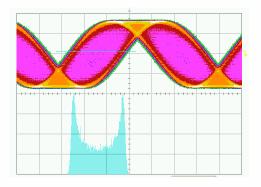

#### **Typical Jittered Signal Waveforms**

The external modulation input can be driven by a function generator such as the Agilent 332XX family of function / arbitrary waveform generators (AWG). The waveform characteristics of the AWG determine the jitter type of the SHF 78210 C.

SHF reserves the right to change specifications and design without notice – SHF 78210 C - V001 – Feb. 12, 2014 Page 7/10

<sup>®</sup> *InfiniBand* is a registered trademark of the InfiniBand Trade Association. *PCI Express* is a registered trademark of Peripheral Component Interconnect Special Interest Group (PCI-SIG).

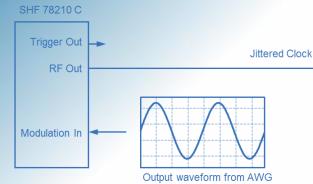

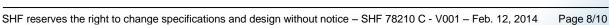

**Sine Wave on Modulation Input**

Sinusoidal jitter on 28 GHz clock.

#### AWG Setting Waveform Sine wave Frequency Amplitude

100 kHz 70 mVpp

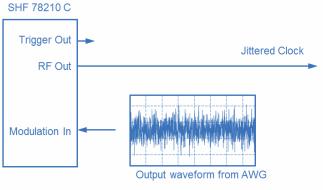

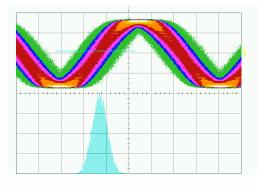

#### **Gaussian-Distributed Noise on Modulation Input**

AWG Setting Waveform Amplitude

Noise 70 mVpp

70 mVpp

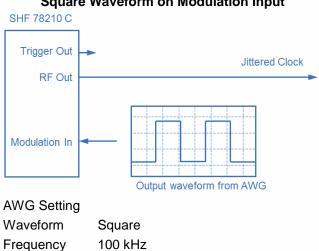

# **Square Waveform on Modulation Input**

Amplitude

Random jitter on 28 GHz clock.

Peak-to-peak jitter on 28 GHz clock.

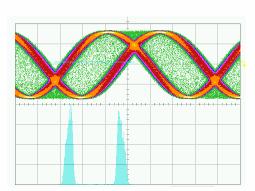

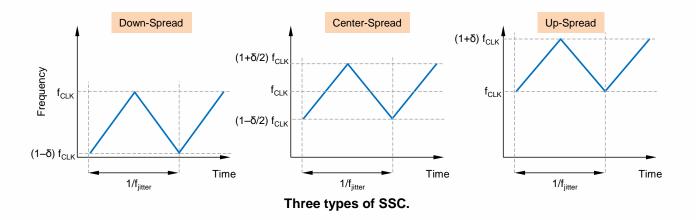

To meet the regulatory demands of electromagnetic interference several high-speed bus systems use a spread spectrum clocking (SSC) method. When SSC is enabled, the instantaneous frequency of the clock signal varies periodically with time by a small amount, i.e. the clock signal is frequency-modulated. The figure below illustrates the SSC frequency modulation with a triangular shape.

The principle of SSC is the periodic frequency modulation of a clock signal.

The key SSC parameters are the following:

- $f_{\text{CLK}} \qquad \text{original clock frequency without SSC}$

- δ relative frequency deviation (often given in percent or ppm, parts per million)

- f<sub>jitter</sub> modulation frequency.

The parameters are directly accessible in the BERT Control Center software GUI or through remote programming.

Depending on the relative position of the clock frequency and the frequency deviation, SSC can be classified into three types: down, center, and up-spread. The figure below illustrates the three configurations.

SHF reserves the right to change specifications and design without notice – SHF 78210 C - V001 – Feb. 12, 2014 Page 9/10

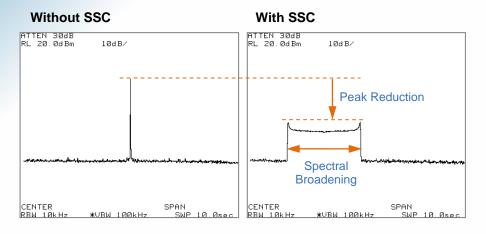

SSC, effectively, broadens the spectral peak of a clock signal so that the maximum of the power spectral density is reduced leading to less radiated emission. This is illustrated in the following spectra measured at the output of the SHF 78210 C for a 25 GHz clock with 30 kHz modulation frequency and 0.5% deviation. Note that SSC does not reduce the total signal power of the clock. Rather, it redistributes the clock's spectral components as shown in the figure below.

SHF 78210 C clock spectrum with and without SSC.

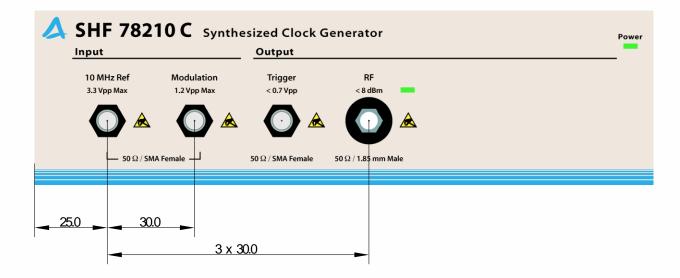

## **Mechanical Drawing**

All dimensions are specified in millimeters (mm).