#### **SHF Communication Technologies AG**

Wilhelm-von-Siemens-Str. 23D • 12277 Berlin • Germany

Phone +49 30 772051-0 • Fax +49 30 7531078

E-Mail: sales@shf.de • Web: http://www.shf.de

# Preliminary Datasheet SHF 615 A

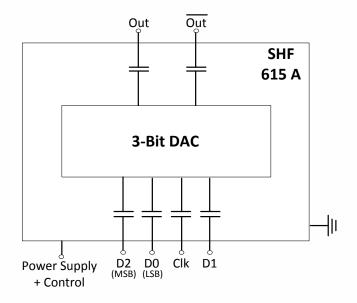

60 GBaud 3-Bit DAC

## **Description**

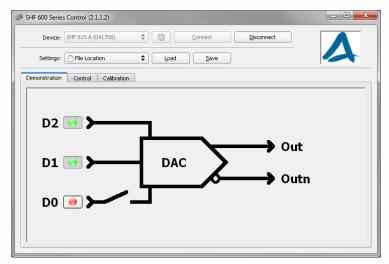

The SHF 615 A is a 3-Bit Digital-to-Analog Converter (DAC) operating at symbol rates up to 60 GBaud for use in broadband test setups and telecom transmission systems. Up to three single ended serial data streams are accepted by the DAC and converted into one differential 8-level data signal. By using two input ports only it is possible to generate 4-level output signals. A single ended clock signal with the same frequency as the data rate drives the SHF 615 A.

For data regeneration purposes all input data signals are re-sampled to mitigate any signal impairments resulting e.g. from long cables. Therefore, it becomes possible to place the DAC very close to the DUT.

All RF input and output ports are AC-coupled.

#### **Features**

- Broadband operation up to 60 GBaud

- Differential data output, 4.8 V differential output swing (2.4V in single-ended operation)

- Single-ended clock and data inputs

- Latched input ports

- Output level control

## **Applications**

- 100, 200, 400 Gbps and 1 Tbps system evaluation & development

- · Broadband test and measurement equipment

- PAM-N, OFDM, Advanced Modulation Experiments

## **Block Diagram**

#### **Ease of Use**

In addition to the DAC itself, the power supply, USB cable, head sink and control software are a complementary part of each delivery. It is recommended to use the DAC only with the delivered power supply module.

The easy to use software package, the SHF 600 Series Control, is the most convenient way to control the DAC. The software reads the individual calibration tables of the DAC and sets the contribution of the bias voltages accordingly. The amplitude of the individual eye openings can be set and is displayed in the graphical user interface (GUI). The enables the user to generate a perfect signal just by a few intuitive clicks. The control software for other operating systems is available on request.

Fig. 2: "SHF 600 Series Control" - GUI

The heat sink can be removed by the customer. In this case it is required to provide other cooling measures to ensure that the maximum case temperature specified on page 4 will not be exceeded.

# **Absolute Maximum Ratings**

| Parameter                              | Unit      | Symbol                             | Min.      | Тур. | Max.      | Comment           |

|----------------------------------------|-----------|------------------------------------|-----------|------|-----------|-------------------|

| Input Parameters                       |           |                                    |           |      |           |                   |

| Data Input Voltage                     | $mV_{pp}$ | V <sub>data in</sub>               |           |      | 900       |                   |

| Clock Input Voltage                    | $mV_{pp}$ | V <sub>clk in</sub>                |           |      | 900       |                   |

| External DC Voltage on RF Input Ports  | V         | $V_{DCin}$                         | -10       |      | +10       | AC coupled input  |

| External DC Voltage on RF Output Ports | V         | $V_{DCout}$                        | -10       |      | +10       | AC coupled output |

| DC Supply Voltages (DAC-Module)        | V         | V <sub>ee</sub><br>V <sub>cc</sub> | -5.0<br>0 |      | 0<br>+6.0 |                   |

## **Specifications**

| Parameter                | Unit               | Symbol               | Min. | Тур.   | Max.    | Comment                                                     |

|--------------------------|--------------------|----------------------|------|--------|---------|-------------------------------------------------------------|

| Input Parameters         |                    |                      |      |        |         |                                                             |

| Data Input Voltage       | $mV_{ampl}$        | V <sub>data in</sub> | 300  |        | 800     | 500 mV recommended                                          |

| Clock Input Frequency    | GHz                | f <sub>in</sub>      | 1    |        | 60      |                                                             |

| Clock Input Voltage      | $mV_{ampl}$        | V <sub>clk in</sub>  | 300  |        | 800     | 500 mV recommended                                          |

| <b>Output Parameters</b> |                    |                      |      |        |         |                                                             |

| Minimum Output Data Rate | GBaud              | $R_{\text{out,min}}$ |      |        | 1       |                                                             |

| Maximum Output Data Rate | Gbaud              | R <sub>out,max</sub> | 60   | 62     |         |                                                             |

| Output Amplitude         | mV <sub>ampl</sub> | V <sub>out</sub>     | 2200 | 2415   |         | Single ended, full scale, adjustable up to -6dB, see page 5 |

| Rise Time <sup>1</sup>   | ps                 | t <sub>r</sub>       |      | 8      | 10      | 20% / 80%                                                   |

|                          |                    |                      |      | 12     | 13      | 10% / 90%                                                   |

| Fall Time <sup>1</sup>   | ps                 | t <sub>f</sub>       |      | 6<br>9 | 8<br>11 | 20% / 80%<br>10% / 90%                                      |

| Differential Output Skew | ps                 | t <sub>skew</sub>    |      | ±1     | ±2      |                                                             |

<sup>&</sup>lt;sup>1</sup> Refers to full scale output swing (measured with a 0101-pattern, phase-synchronized at all data input ports)

| Power Requirements (incl. Power Supply) |    |                   |       |      |       |                                       |

|-----------------------------------------|----|-------------------|-------|------|-------|---------------------------------------|

| Supply Voltage                          | V  | V <sub>c</sub>    | +11.5 | +12  | +12.5 |                                       |

| Supply Current                          | mA | Ic                |       | 650  |       |                                       |

| Power Dissipation                       | W  | P <sub>d</sub>    |       | 7.8  |       | @ V <sub>C</sub> = +12V               |

| Power Requirements (DAC-Module only)    |    |                   |       |      |       |                                       |

| Supply Voltage                          | V  | V <sub>ee</sub>   | -4.6  | -4.4 | -4.3  |                                       |

| Supply Current                          | mA | l <sub>ee</sub>   |       | 1050 | 1150  |                                       |

| Supply Voltage                          | V  | V <sub>cc</sub>   | +5.2  | +5.3 | +5.5  |                                       |

| Supply Current                          | mA | I <sub>cc</sub>   |       | 320  | 350   |                                       |

| Power Dissipation                       | W  | P <sub>d</sub>    |       | 6.3  |       | @ $V_{EE} = -4.4V$ , $V_{CC} = +5.3V$ |

| Conditions                              |    |                   |       |      |       |                                       |

| Case Temperature <sup>2</sup>           | °C | T <sub>case</sub> | 10    |      | 45    |                                       |

## **Typical Output Amplitudes**

Below mentioned values assume no attenuation to be set in the control software. The output amplitude of the DAC can be reduced by 0 to -6 dB by making the appropriate setting in the control software.

| Input D2 | Input D1 | Input D0 | Typical Output<br>Amplitude [mV] |

|----------|----------|----------|----------------------------------|

| -        | -        | On       | 345                              |

| -        | On       | -        | 690                              |

| On       | -        | -        | 1380                             |

The typical output amplitude of a multilevel signal can be calculated by accumulating the typical output amplitudes of all applied input ports of the DAC as shown in the table above. Thus the full scale output swing (all inputs active) accumulates as follows:

| On On | On | 2415 |

|-------|----|------|

|-------|----|------|

<sup>&</sup>lt;sup>2</sup> Tr / Tf of the output data signal can be slightly decreased by applying additional cooling measures like heat sinks or cooling fans.

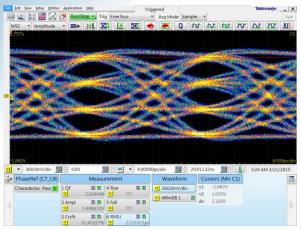

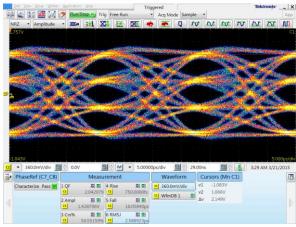

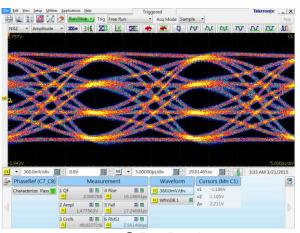

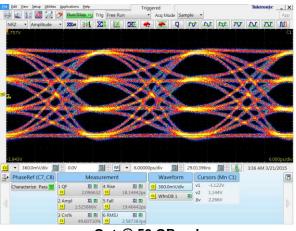

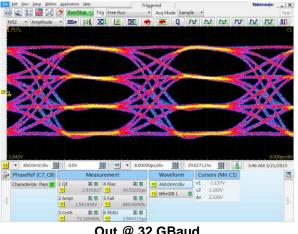

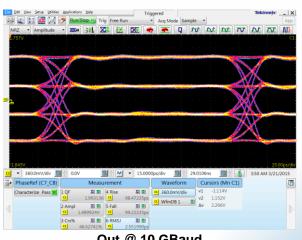

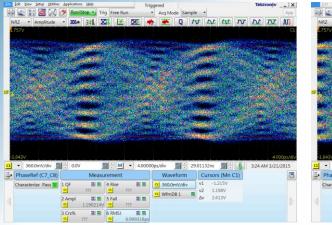

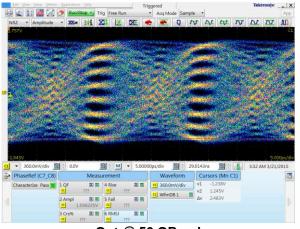

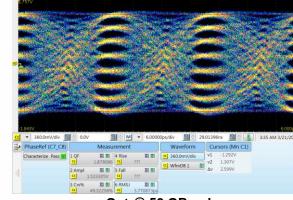

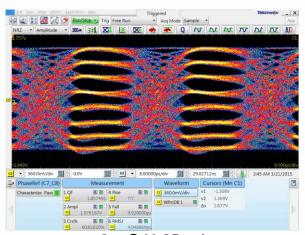

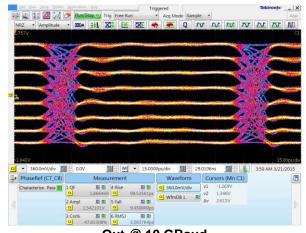

### **Typical Output Eye Diagrams**

The measurements below had been performed using a SHF 12104 A Bit Pattern Generator (PRBS 2<sup>31</sup>-1) and a Tektronix DSA 8300 Digital Serial Analyzer (DSA) with Phase Reference Module (82A04B-60G) and 70 GHz Sampling Module (80E11). The outputs of the DAC module had been connected directly to the DSA input with a 20 dB attenuator.

#### 4-Level Output Signal Measurement

Out @ 62 GBaud

Out @ 60 GBaud

Out @ 56 GBaud

Out @ 50 GBaud

Out @ 32 GBaud

Out @ 10 GBaud

SHF reserves the right to change specifications and design without notice - SHF 615 A - V001 - March 20, 2015

#### **8-Level Output Signal Measurement**

| Triggered | Tektronix | 2| 2 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 | 3| 1 ☐ • 360.0mV/div ☐ PhaseRef (C7\_C8)

Out @ 62 GBaud

Out @ 60 GBaud

Edit Siev Steip Beller Spread Trig Free Run

Out @ 56 GBaud

Out @ 50 GBaud

Out @ 32 GBaud

Out @ 10 GBaud

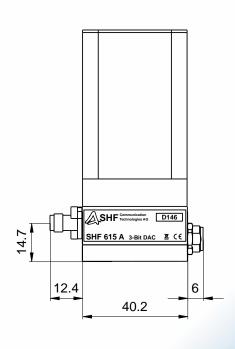

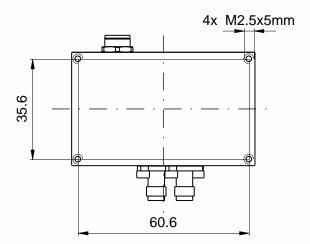

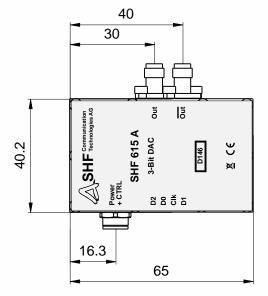

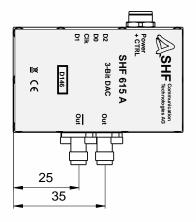

# **Outline Drawing - Module**

All dimensions in mm.

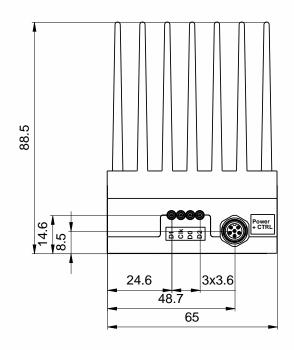

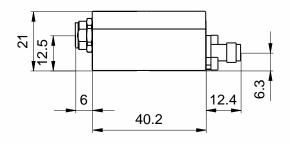

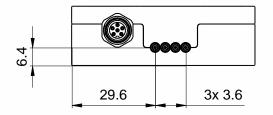

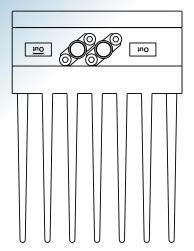

# Outline Drawing - Module with Heat Sink

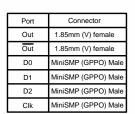

| Port | Connector           |

|------|---------------------|

| Out  | 1.85mm (V) female   |

| Out  | 1.85mm (V) female   |

| D0   | MiniSMP (GPPO) Male |

| D1   | MiniSMP (GPPO) Male |

| D2   | MiniSMP (GPPO) Male |

| Clk  | MiniSMP (GPPO) Male |

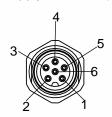

| Power Supply & Control (I2C-Bus) |        |             |  |  |

|----------------------------------|--------|-------------|--|--|

| Pin                              | Colour | Designation |  |  |

| 1                                | brown  | SCL         |  |  |

| 2                                | white  | Vcc         |  |  |

| 3                                | blue   | GND         |  |  |

| 4                                | black  | Vee         |  |  |

| 5                                | grey   | SDA         |  |  |

| 6                                | pink   | GND         |  |  |

All dimensions in mm.